# **WELCOME TO ICECS 2012**

On behalf of the Organizing Committee of ICECS 2012, and of my co-chairs Dr. Manuel Delgado-Restituto and Prof. Magdy Bayoumi, it is my pleasure to welcome you to the 19th International Conference on Electronics, Circuits, and Systems, to Seville and to Spain. ICECS 2012, sponsored by the Institute of Electrical and Electronics Engineers, is the flagship conference of the IEEE Circuits and Systems Society in Region 8. The ICECS series of conferences have evolved during nearly two decades to become a major networking event for those working on CASS topics, from analog and RF circuits to VLSI signal processing, including biomedical, emerging technologies, CAD, nonlinear and neural networks, etc. As a delegate at ICECS 2012 you will have the opportunity to learn of the latest advances in these fields, and to meet those who have dared, pioneered, and succeeded.

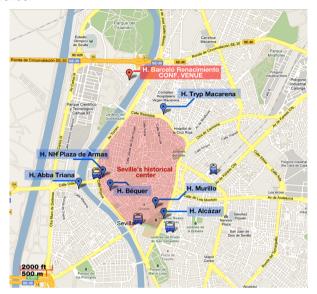

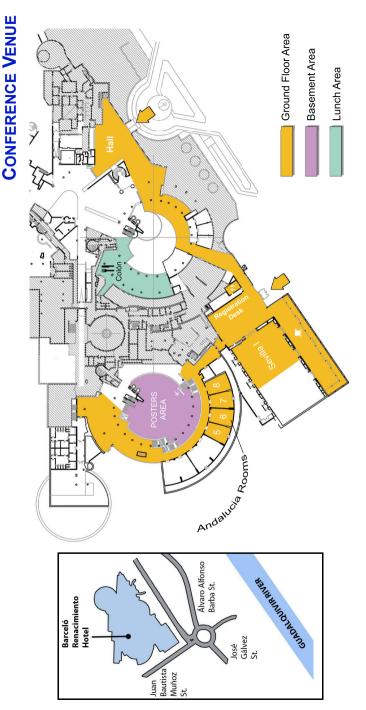

The conference is to be held at the Barceló Hotel Renacimiento, on the Isla de la Cartuja, an island located between two branches of the Guadalquivir river which today is home to the Cartuja 93 technology business park. Seville's downtown (El Centro) is very close by and, from there, visitors will find Seville's major monuments and shops just a few short steps away.

This year, a total of 380 submissions from 51 different countries were received including 222 papers from Europe, 61 from Asia-Pacific, 28 from North America, 26 from Latin America and 43 from the Middle East and Africa. This is proof of the truly international nature of this event.

The Technical Program has been selected with the inestimable, volunteer support of 31 Track Chairs coordinated by Prof. de la Rosa and Prof. Setti; many thanks to all them. They have been backed by more than 300 anonymous reviewers whose contribution has been instrumental for the conference. Three plenary presentations by guest speakers complete the program by focusing on highly relevant topics selected by an ad-hoc committee. I would like to thank these guest speakers for their availability.

As a novelty this year, seven Tutorials covering a variety of topics will be made available for free to all attendees. The service to society rendered by these lecturers in making their expertise openly available deserves my highest recognition.

I would also like to thank the Steering Committee of ICECS for giving us the opportunity to host this event. The conference has been organized by members of the Institute of Microelectronics

# **WELCOME TO ICECS 2012**

of Seville (IMSE-CNM), the Spanish Council of Research (CSIC) and the University of Seville. I would like to thank the authorities of these institutions for allowing all us to devote part of our time to the organization of this conference.

Many thanks as well to my Conference Co-Chairs, Dr. Manuel Delgado-Restituto and Prof. Magdy Bayoumi for their inestimable advice and support. The three of us have been extremely fortunate to count on an outstanding team of volunteers of the Organizing Committee, who have all worked very hard. We are hugely indebted to all these volunteers. Our warm thanks to all of them for their dedication, enthusiasm and professionalism.

Last but not least, we would like also to express our greatest appreciation to all the authors who submitted papers to the conference and to all delegates, tutorial lecturers and plenary speakers who have travelled to Seville to interact and share their thoughts during the Conference. They will play a leading role at the event.

Enjoy ICECS 2012 and your visit to Seville. I hope to see you all back here more often!

Welcome / Bienvenidos !!

Ángel Rodríguez-Vázquez University of Seville General Chair - ICECS 2012

# **ABOUT IMSE/US**

The "Instituto de Microelectrónica de Sevilla" (IMSE) is a R&D center specialized on design and test of analog, mixed-signal, and sensory-processing integrated circuits as well as on their use in any application context, specially in RF, microsystems, data conversion, ...

IMSE, together with the Microelectronics Institutes in Barcelona (IMB) and Madrid (IMM), form the Spanish National Microelectronics Center (CNM) operated under the umbrella of "Consejo Superior de Investigaciones Científicas" (CSIC).

The personnel from IMSE has been carrying out research, teaching, and technology transfer for more than 20 years. In particular, teaching is done as regular courses offered by the University of Seville and as courses and seminars given elsewhere on demand. The PhD thesis and the research projects within IMSE are mainly focusing on the implementation of innovative concepts in silicon, paying special attention to their experimental verification.

Starting on 2009, IMSE is providing external services based on a tester Agilent 93000, giving training, technical support, and test-board design for implementing and debugging test procedures both in analog and digital.

In addition, IMSE offers an academic master: Master in Microelectronics Design and Applications of Micro/Nanometric Systems. It is oriented to provide professionals with a scientific, technological, and sociol-economic education in Micro-Nano electronics.

On the other hand, the "Universidad de Sevilla" (US) is a topranked European university. Founded under the name of Colegio Santa María de Jesús in 1505, the University of Seville, with a student body of over 55,000, is one of the most important higher education institutions in the country.

The Faculties, Technical High Schools, Polytechnics and University Schools are the centers in charge of organizing the teaching as well as the academic, administrative, and managerial processes leading to obtaining a degree.

Public service of higher education is assigned to this university and carried out through the study, teaching and research as well as through the generation, development and diffusion of knowledge at society and citizenship's service, offering as well, scientific and technical support for the cultural, social, economic and territorial development and the concern for training professionals.

# CONTENTS

| Overview of ICECS 2012      | 5  |

|-----------------------------|----|

| Conference Schedule         | 6  |

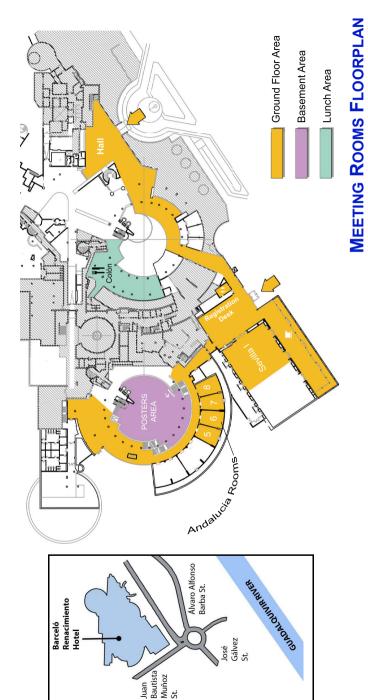

| Meeting Rooms Floorplan     | 7  |

| Program at a Glance         | 8  |

| Committees                  | 12 |

| Welcome to Sevilla          | 16 |

| Conference Venue            | 21 |

| Conference Information      | 27 |

| Meals and Refreshments      | 29 |

| Social Program              | 30 |

| Optional Leisure Activities | 32 |

| Plenary Lectures            | 35 |

| Tutorials                   | 39 |

| Lecture Sessions            | 48 |

| PhD Competition             | 93 |

| Poster Sessions             | 95 |

| Notes                       | 99 |

## **OVERVIEW OF ICECS 2012**

The IEEE International Conference on Electronics, Circuits, and Systems (ICECS) is the flagship conference of the IEEE Circuits and Systems (CAS) Society in Region 8 of IEEE (Europe, Middle East, and Africa). Papers from all over the world are presented on design methodologies, techniques and experimental results in emerging electronics, circuits, and systems.

#### **TECHNICAL SESSIONS**

IEEE ICECS 2012 sessions will cover all aspects of the fields of electronics, circuits, and systems, including analog and digital electronics, solid-state circuits, green and power electronics, biomedical and life-science circuits and systems. Topics include, but are not limited to:

- Analog & Mixed Signal Circuits and Signal Processing

- Bioengineering Circuits and Systems

- Circuits and Systems for Communications

- Digital Circuits and Signal Processing

- Emerging Technologies (Nano, MEMS)

- Low-Power and Harvesting Techniques

- Multimedia Systems and Signal Processing

- Neural Network Circuits and Systems

- Nonlinear Circuits and Systems

- Photonic and Optoelectronic Circuits

- Sensing and Sensor Networks

- Test and Reliability

- VLSI Systems, Applications, and Computer Aided Network Design

#### **PLENARY LECTURES**

In addition to contributed papers, the event will include plenary lectures and tutorials. Three exciting plenary lectures presented by world-wide recognized experts has been organized to cover hot topics in the circuits and systems field.

#### **TUTORIALS**

In an attempt to increase the number of attendees and create a fruitful pre-conference atmosphere, the Organization has made a great effort to offer these short courses for free. The seven tutorials are scheduled.

#### SOCIAL PROGRAM

An attractive social program will accompany the event, featuring a welcome reception, a gala dinner, a farewell reception, and excursions.

# **CONFERENCE SCHEDULE**

#### Sunday, December 9th, 2012

| 09:00 | Morning | <b>Tutorials</b> |

|-------|---------|------------------|

|-------|---------|------------------|

11:00 Break

11:30 Morning Tutorials (cont.)

15:00 Afternoon Tutorials

17:00 Break

17:30 Afternoon Tutorials (cont.)

## Monday, December 10th, 2012

| 08:15 | Conference Opening |

|-------|--------------------|

| 08:30 | Plenary Lecture    |

| 09:30 | Lecture Sessions   |

| 11:10 | Coffee Break       |

| 11:30 | Lecture Sessions   |

| 42.40 | Lunah              |

13:10 Lunch

14:40 Lecture Sessions 16:20 Coffee Break

16:40 Poster Briefing Session 1

17:10 Lecture Sessions19:30 Welcome Reception

#### Tuesday, December 11th, 2012

| 08:30 | Plenary Lecture  |

|-------|------------------|

| 09:30 | Lecture Sessions |

| 11:10 | Coffee Break     |

| 11:30 | Lecture Sessions |

| 42.40 | Lunah            |

13:10 Lunch

14:40 Lecture Sessions 16:20 Coffee Break

16:40 Poster Briefing Session 2

17:10 PhD Competition and Poster Exhibition

19:30 Gala Dinner

# Wednesday, December 12th, 2012

Closing Ceremony

| 08:30 | Plenary Lecture         |

|-------|-------------------------|

| 09:30 | <b>Lecture Sessions</b> |

| 11:10 | Coffee Break            |

| 11:30 | Lecture Sessions        |

| 13:10 | Lunch                   |

| 14:40 | Lecture Sessions        |

| 16:20 | Coffee Break            |

| 16:40 | Lecture Session         |

18:20

# **MEETING ROOMS FLOORPLAN**

| Room Andalucía 5 Advances In Time-Encoded Analog Signal Processing and Data Conversion L. Hernández, S. Paton, E. Prefasi (Carlos III Univ.) - P. Rombouts (Gent Univ.) | TUTORIAL 1  Advances in Time-Encoded Analog Signal Processing and Data Conversion  Emerging Technology U. Hermändez, S. Paton, E. Prefasi (Carlos III Henry H. Radamson, Lars Thylén (KTH))  BRR TIMPRIAL 1 (Cont.)  TIMPRIAL 1 (Cont.) | Room Andalucía 7  TUTORIAL 3  RF CMCS Wireless Receivers for 402MHz  Medical Implantable Communication Systems S. Mohamed, Y. Manoli (Albert-Ludwig-University Freiburg)                                                        | Room Andalucía 8                                                                                                                                                                                                             |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| e-Encoded Analog Signal<br>Data Conversion<br>Paton, E. Prefasi (Carlos III                                                                                             | BB.                                                                                                                                                                                                                                     | UTORIAL 3 FF CMOS Wireless Receivers for 402MHz Medical implantable Communication Systems 5. Mohamed, Y. Manoli Albert-Ludwig-University Freiburg)                                                                              |                                                                                                                                                                                                                              |

| Paton, E. Prefasi (Carlos III<br>outs (Gent Univ.)                                                                                                                      | 8                                                                                                                                                                                                                                       | غ. Mohamed, Y. Manoli<br>Albert-Ludwig-University Freiburg)                                                                                                                                                                     |                                                                                                                                                                                                                              |

|                                                                                                                                                                         | 18                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                              |

|                                                                                                                                                                         |                                                                                                                                                                                                                                         | BREAK                                                                                                                                                                                                                           |                                                                                                                                                                                                                              |

| 11:30-13:00 TUTORIAL 1 (sont.)                                                                                                                                          |                                                                                                                                                                                                                                         | TUTORIAL 3 (cont.)                                                                                                                                                                                                              |                                                                                                                                                                                                                              |

|                                                                                                                                                                         |                                                                                                                                                                                                                                         |                                                                                                                                                                                                                                 |                                                                                                                                                                                                                              |

| TUTORIAL 4 Digital Delta-Sigma Modulators for DAC and Fractional-N Frequency Synthesis Annications                                                                      |                                                                                                                                                                                                                                         | TUTORIAL 6  Memristor Technology in Neuromorphic Circuits Low Power Design Methodology and Techniques – Industrial Perspective                                                                                                  | TUTORIAL 7<br>Low Power Design Methodology and<br>Techniques – Industrial Perspective                                                                                                                                        |

| Michael Peter Kennedy (Univ. College Cork)                                                                                                                              |                                                                                                                                                                                                                                         | Fernando Corinto (Politecnico di Torino)                                                                                                                                                                                        | Kaijian Shi (Cadence Design Systems, USA)                                                                                                                                                                                    |

|                                                                                                                                                                         | BRI                                                                                                                                                                                                                                     | EAK                                                                                                                                                                                                                             |                                                                                                                                                                                                                              |

| 17:30-19:00 TUTORIAL 4 (cont.)                                                                                                                                          | TUTORIAL 5 (cont.)                                                                                                                                                                                                                      |                                                                                                                                                                                                                                 | TUTORIAL 7 (cont.)                                                                                                                                                                                                           |

|                                                                                                                                                                         | na Modulators for DAC and luency Synthesis nnedy (Univ. College Cork)                                                                                                                                                                   | Modulators for DAC and Using Logical Effort for Designing Carbon noy Synthesis Nanotube FET (CNFET)-based Digital Circuits Malgorzata Chrzanowska-Jeske edy (Univ. College Cork) (Portland State Univ.)  RR  TUTORIAL 5 (cont.) | Modulators for DAC and Using Logical Effort for Designing Carbon Incy Synthesis Nanotube FET (ONFET)-based Digital Circuits Malgorzata Chrzanowska-Jeske edy (Univ. College Cork) (Portland State Univ.)  TUTORIAL 5 (cont.) |

**VELCOME RECEPTION**

#### Advances in Embedded Vision Computationally Intensive Room Andalucía 5 Applications on FPGAs A4L-E (SPECIAL SESSION) A1L-E (SPECIAL SESSION) **Hardware** ROOM Sevilla I - PLENARY LECTURE: Ultra-Low Power Circuit Techniques for Implanted/Medical Applications RF and mmWave Circuits Room Andalucía 6 **Wireless and Wireline** ROOM Sevilla I - CONFERENCE OPENING (Prof. Ángel Rodríguez-Vázquez) RF Building Blocks Communications Communications Algorithms for ATP A2L-D SPEAKER: Prof. Yusuf Leblebici (EPFL) /LSI Digital Implementations MONDAY, DECEMBER 10th, 2012 Digital Signal Processing Digital Circuits on FPGAs Room Andalucía 7 COFFEE BREAK COFFEE BREAK Analog Circuits and Techniques Sensing and Sensor Networks DSP Algorithm and LUNCH nplementation AILC Analog Circuits and Techniques Bioengineering Circuits and Room Andalucía 8 Analog Circuits and Techniques Sensors and Photonics **Mixed-Signal Test and** /erification Systems I A2L-B Poster Briefing Session 1 Room Sevilla I **Analog Filters** AL-A 9:30-11:10 A1L-A 16:40-17:10 B4P-G 11:30-13:10 A2L-A 14:40-16:20 A3L-A 11:10-11:30 13:10-14:40 16:20-16:40 17:10-18:50 38:15-08:30 30-09:20 ame Tame

PROGRAM AT A GLANCE

19:30

# PROGRAM AT A GLANCE

|                                |                                           | TUESDAY, DECEMBER 11th, 2012                                                              | 11th, 2012                                                                                  |                                                       |

|--------------------------------|-------------------------------------------|-------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|-------------------------------------------------------|

| TIme                           | Room Sevilla I                            | Room Andalucía 8                                                                          | Room Andalucía 7                                                                            | Room Andalucía 6                                      |

| 08:30-09:20                    |                                           | ROOM Sevilla I - PLENARY LE<br>SPEAKER: Dr. EI                                            | ROOM Sevilla I - PLENARY LECTURE: From Data to Insight<br>SPEAKER: Dr. Ellen J. Yoffa (IBM) |                                                       |

| 09:30-11:10 B1L-A              | <b>B1LA</b><br>Data Converters            | Bloengineering Circuits and Systems II Digital Circuits for Embedded Control and Security | B1LC (SPECIAL SESSION) Digital Circuits for Embedded Control and Security                   | <b>B1L-D</b><br>Digital Circuits for Channel Coding   |

| 11:10-11:30                    |                                           | COFFEE                                                                                    | COFFEE BREAK                                                                                |                                                       |

| 11:30-13:10 B2L-A              | B2LA<br>Oversampling Data Converters      | B2LB<br>Analysis and Design for Low-Power<br>Circuits                                     | B2LC<br>Circuit Level CAD                                                                   | <b>B2LD</b> Nonlinear Circuits and Systems I          |

| 13:10-14:40                    |                                           | רחנ                                                                                       | LUNCH                                                                                       |                                                       |

| 14:40-16:20 B3L-A<br>Nyqui     | B3LA<br>Nyquist Rate Data Converters      | <b>B3LB</b><br>Circuit Techniques for Energy<br>Harvesting Applications                   | B3LC Methodologies for Systems-on-Chip                                                      | B3LD<br>Multimedia Systems and Signal<br>Processing I |

| 16:20-16:40                    |                                           | COFFEE                                                                                    | COFFEE BREAK                                                                                |                                                       |

| <b>16:40-17:10 B4P-H</b> Poste | <b>B4P-H</b><br>Poster Briefing Session 2 |                                                                                           |                                                                                             |                                                       |

| 17:10-19:10 BA4L-A             | BA4L-A<br>PhD Competition                 |                                                                                           | Poster area - POSTER EXHIBITION                                                             |                                                       |

| 19:30                          |                                           | GALA                                                                                      | GALA DINNER                                                                                 |                                                       |

# **PROGRAM AT A GLANCE**

|                               |                                               | WEDNESDAY, DECEMBER 12th, 2012                                                                                                          | R 12th, 2012                                                                                                          |                                                                 |

|-------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|

| TIMe                          | Room Sevilla I                                | Room Andalucía 8                                                                                                                        | Room Andalucía 7                                                                                                      | Room Andalucía 6                                                |

| 08:30-09:20                   | RO                                            | ROOM Sevilla I - PLENARY LECTURE: Compressed Sensing Analog-to-Digital Conversion SPEAKER: Prof. Michael Flynn (University of Michigan) | PLENARY LECTURE: Compressed Sensing Analog-to-Digital Conver<br>SPEAKER: Prof. Michael Flynn (University of Michigan) | sion                                                            |

| 09:30-11:10 C1L-A             | <b>C1L-A</b><br>RF Circuits and Techniques I  | <b>C1L-B</b><br>Emerging Technologies I                                                                                                 | CALC<br>Digital Test, Fault Tolerance and<br>Reliability                                                              | C1L-D<br>Multimedia Systems and Signal<br>Processing II         |

| 11:10-11:30                   |                                               | COFFEE                                                                                                                                  | COFFEE BREAK                                                                                                          |                                                                 |

| 11:30-13:10 C2L-A             | <b>C2L-A</b><br>RF Circuits and Techniques II | <b>c21-8</b><br>Emerging Technologies II                                                                                                | <b>c2L-C</b><br>Variability-Aware Design and Noise<br>Mitigation                                                      | <b>C2L-D</b><br>Nonlinear Circuits and Systems II               |

| 13:10-14:40                   |                                               | הח                                                                                                                                      | LUNCH                                                                                                                 |                                                                 |

| 14:40-16:20 <b>C3L-A</b> Powe | <b>cal-A</b><br>Power Management Circuits     | <b>c3LB</b><br>Neural Networks and Nonlinear<br>Circuits                                                                                | C3LC Energy Efficient High-Level Design and Communication Algorithms and Modeling Techniques  Building Blocks         | <b>ca.p.</b><br>Communication Algorithms and<br>Building Blocks |

| 16:20-16:40                   |                                               | COFFEE                                                                                                                                  | COFFEE BREAK                                                                                                          |                                                                 |

| 16:40-18:20 C4L-A             | <b>CALA</b><br>Sensors and Imagers            | C4L8 (SPECIAL SESSION) Advances in Nanoscale Devices and Circuits: Modeling, Design, Testing                                            | <b>CALC</b> Algorithms and Processors                                                                                 |                                                                 |

| 18:20                         |                                               | ROOM Sevilla I - CLOSING CEREMO                                                                                                         | ROOM Sevilla I - CLOSING CEREMONY (Prof. Ángel Rodríguez-Vázquez)                                                     |                                                                 |

#### **ORGANIZATION COMMITTEE**

General Chairs Ángel Rodríguez-Vázguez

University of Seville & IMSE-

CNM-CSIC, Spain

Manuel Delgado-Restituto IMSE-CNM-CSIC, Spain

Magdy Bayoumi

University of Louisiana, USA

**Technical Program Chairs** José M. de la Rosa

University of Seville & IMSE-

CNM-CSIC, Spain

Gianluca Setti

University of Ferrara, Italy

**Special Session Chairs** Mohammed Ismail

> Ohio State University, USA Currently with KUSTAR, UAE

Esteban Tielo Cuautle

INAOE, Mexico

Plenary Lectures and

**Tutorial Chairs**

Maciej Ogorzalek

Jagiellonian University, Polland

Manuel Delgado-Restituto IMSE-CNM-CSIC, Spain

#### **LOCAL ORGANIZATION COMMITTEE**

#### **CONFERENCE VENUE AND INFRASTRUCTURE CHAIRS**

Gustavo Liñán Cembrano, IMSE-CNM-CSIC Ricardo Carmona Galán. IMSE-CNM-CSIC

#### CONFERENCE SECRETARY AND FINANCE CHAIR

Óscar Guerra Vinuesa, Univ. of Seville & IMSE-CNM-CSIC

#### **PUBLICATION CHAIRS**

Piedad Brox Jiménez, IMSE-CNM-CSIC

Rocío del Río Fernández. Univ. of Seville & IMSE-CNM-CSIC

#### LOCAL ARRANGEMENTS AND REGISTRATION

Óscar Guerra Vinuesa, *Univ. of Seville & IMSE-CNM-CSIC* Javier Bernal Lérida, *University of Seville* Isbilya Travel

#### INTERNATIONAL CONTACT POINTS

Rui Martins, *University of Macau* Ricardo Reis, *Universidade Federal do Rio Grande do Sul* Liviu Goras, "Gheorghe Asachi" Technical University of lasi Mohamad Sawan, École Polytechnique de Montréal

#### **CONFERENCE SECRETARIAT**

Óscar Guerra Vinuesa Instituto de Microelectrónica de Sevilla IMSE-CNM-CSIC

Avda. Américo Vespucio, s/n Isla de la Cartuja 41092 Sevilla, Spain

Phone: +34 95 446 66 66 Fax: +34 954 46 66 69 guerra@imse-cnm.csic.es

#### **LOCAL ORGANIZATION**

#### Isbilya Travel

Avda. Américo Vespucio s/n Isla de la Cartuja 41092 Sevilla, Spain

Phone: +34 95 499 10 68 Fax: +34 954 99 01 93

icecs2012@isbilyatravel.com

#### STEERING COMMITTEE

El Mostapha Aboulhamid *Univ. Montréal*M. Omair Ahmad *Concordia Univ.*Wael Badawy *IntelliView*Herve Barthelemy *Univ. Sud Toulon-Var*Magdy Bayoumi *Univ. I ouisiana*

Magdy Bayoumi Univ. Louisiana

Jean-Baptiste Begueret IMS Lab Bordeaux

Malgorzata Chrzanowska- Portland State Univ.

Jeske

Ahmed Eltawil *Univ. California, Irvine*

Eleni Fotopoulou *Univ. Patras*Eby Friedman *Univ. Rochester*

Georges Gielen Katholieke Univ. Leuven Lorenzo Gonzo Fondazione Bruno Kessler Haidar Harmanani Lebanese American Univ.

Mohammed Ismail Ohio State Univ.

Waleed Khalil Ohio State Univ.

Eric Kerherve IMS Lab Bordeaux

Fadi Kurdahi Univ. California, Irvine

Mourad Loulou Univ. Sfax Univ. Pavia Piero Malcovati Univ. Pavia Franco Maloberti Micallef Univ. Malta Joseph George Mochytz FTH Zürich Monmouth Univ. Mohammad Obaidat Vassilis **Paliouras** Univ Patras

Branimir Pejcinovic Portland State Univ.

Ricardo Reis Univ. Fed. do Rio Grande

do Sul

Ángel Rodríguez- University of Seville

Vázguez

Ana Rusu KTH

Mohamad Sawan École Polytech. de Montréal Andrea Simoni Fondazione Bruno Kessler

Thanos Stouratis *Univ. Patras*M.N.S. Swamy *Concordia Univ.*

Lars Wanhammar Linköpings Universitet

Orly Yadid-Pecht *Univ. Calgary* Amal Zaki *NARSS Egypt*

#### **TECHNICAL PROGRAM COMMITTEE**

Antonio Acosta University of Seville Eduard Alarcón TU Catalunya (UPC)

Massimo Alioto Univ. Siena

Andreas Andreou Johns Hopkins Univ.

Sergio Bampi Univ. Fed. do Rio Grande do Sul

Erik Bruun *TU Denmark*

Andreas Burg *EPFL*Sergio Callegari *Univ. E*

Univ. Bologna IMSF-CNM-CSIC Ricardo Carmona Deming Chen Univ. Illinois at Urbana Timothy Constandinou Imperial College London Fernandes Jorge INESC-ID / IST / TU Lisboa Alexander Fish Ben-Gurion Univ.

Alexander Fish Ben-Gurion Univ.

Anthony Ho Univ. Surrey

Valencia Joyner Tufts Univ.

Rouwaida Kanj American Univ. Beirut Yong Lian Nat. Univ. Singapore Chia-Wen Lin Nat. Tsing Hua Univ.

Antonio López-Martín *Univ. Navarra* Piero Malcovati *Univ. Pavia*

Yehia Massoud Univ. Alabama at Birmingham

Salvador Mir TIMA

Shahriar Mirabbasi *Univ. British Columbia* Yoshifumi Nishio *Tokushima Univ.* Ian O'Connor *École Centrale de Lyon*

Maurits Ortmanns *Univ. Ulm*Giovanni Pazienza *Univ. Pazmany*

Ana Rusu KTH

Fernando Silveira Univ. de la República Mani Soma Univ. Washington

Mikko Valkama Tampere Univ. of Technology

Diego Vázquez University of Seville

Chai Wah Wu IBM

Seville ("Sevilla" in spanish), rich millenary heiress of different cultures that settled along the shores of the Guadalquivir River, preserves and pampers its world famous monumental architecture. At the same time it proudly and brilliantly treasures mysterious secrets that romantic authors attempted to release in mythical works such as Carmen, The Barber of Seville or Don Juan, amongst many others.

Nonetheless, the Seville that we wish to introduce to you today is a synopsis of the values of its past heritage and modernity of its present reality. Such a symbiosis holds the city's historical character which offers contemporary infrastructures which convert the city into a first class tourist destination, not just for the individual tourist but also for the business person attending conferences or incentive trips.

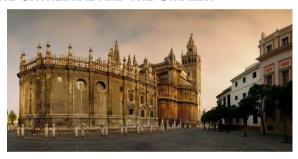

#### THE CATHEDRAL AND THE GIRALDA

"Let us create such a building that future generations will take us for lunatics". That's what churches authorities repudetly agreed back in 1401. And they certainly got themselves the big and magnificent Cathedral, one of the largest catholic churches in the world: the main building is 126m long and 83m wide. The original mosque's beautiful minaret (for the cathedral was built over the main mosque that fell to the christians in 1248), La Giralda, still stands on its eastern side, but the cathedral's bulky exterior gives few other hints of the treasures within.

**Price per person:** €7.50 **Hours:** Mon-Sat: 11:00 - 17:00

Phone: (+34) 954 214 471

#### **ALCÁZAR**

Residence of many generations of kings and caliphs, the not-to-be-missed Alcázar is an intriguing, beautiful complex of gardens, patios, and royal rooms, and it is intimately associated with the lives and loves of many Muslim and Christian rulers, above all Pedro I of Castilla, who was known as Pedro El Cruel and Pedro El Justiciero (the Cruel and the Justice-dispenser) depending which side of him you were on.

Price per person: €7

Hours: Thu-Sat: 09:30 - 17:00. Sun: 09:30 - 13:30

**Phone:** (+34) 954 502 324

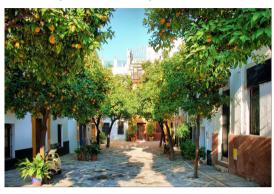

#### SANTA CRUZ, THE CENTRO, AND THE ARENAL

Santa Cruz is Seville's medieval Judería (Jewish quarter), today a tangle of quaint, winding streets and lovely plant-decked plazas perfumed with orange blossom. Plaza de Santa Cruz, Plaza Doña Elvira, the 17th-century Hospital de los Venerables Sacerdotes, are spots the visitor won't want to miss here. The real center of Sevilla, El Centro, is densely packed with narrow streets and broken up by squares and streets (Calle Sierpes, Casa Pilatos, Plaza del Salvador, ...) around which the city's life has revolved for aeons. The Arenal, a short walk from the Cathedral, brings the visitor to the Río Guadalquivir. Seville's most interesting sights here include the Torre del Oro (a 13th-century islamic watch tower), Plaza de Toros (the bullring, one of the most handsome in Spain and probably the oldest), the Hospital de la Caridad and the Museo de Bellas Artes (Fine-Arts Museum), which is the second Art Gallery in the country.

#### CLIMATE

Seville has a Mediterranean weather due to the oceanic influences nearby. In the winter the temperatures are mild, and in the summer the weather is hot. Precipitation varies along the year, concentrated in the period October to April. December is the wettest month, and the coldest are January and February. June, July, and August are the hottest months.

#### **FAST FACTS**

Country: Spain / España

Status: city / capital of Andalusia

Population: 720,000 in the city + another 400,000 in its

outskirts

Language: Spanish

Time zone: UTC+2 at summer time (March 28 to October 31),

UTC+1 at winter time (From October 31)

Country dialling code: +34

Telephone area code for Seville: 95

**Currency:** Euro is the official currency of Spain. Euro (€) = 100 cents. Notes are in denominations of €500, 200, 100, 50, 20, 10, and 5. Coins are in denominations of €2, €1, and 50, 20, 10, 5, 2, and 1 cents. Money can be taken from cash machines (ATMs) which accept most international cards.

#### Health and security:

- Emergency service (Fireman, police, civil protection, sanitary emergency) phone number: 112

- National police: emergency telephone number: 091

- Local police: emergency telephone number: 062

- Medical emergencies: emergency telephone number: 061

**Tipping:** tipping in Spain is not obligatory but it is common to leave some change or to give a tip of 5–10%. There are no added service charges on the final bill at any hotel, restaurant, or bar.

**Electricity:** 220 volts, 50 Hz - round two-pin plugs are used **Measures:** Weight measured in kilograms, distances measured by the metric system, temperature measured in degrees Celsius **Tourism: Over** 2 million tourists visit Seville Province each year.

Tourist Office: Paseo de las Delicias, 9 (Costurero de la Reina)

41012 Sevilla. Phone: +34 954 234 465 Seville tourism information can be found at: www.turismosevilla.org, www.andalucia.org

#### **PHARMACIES**

A chemist's or drugstore is known as a Farmacia and they can be identified by a large green or red cross sign outside. They tend to keep the same working hours as other shops and if closed, usually display a sign indicating the nearest pharmacy that is open. As well as selling prescription medicines, they also offer free advice about minor injuries or ailments and they will happily suggest non-prescription treatments. Usually open from 9.30am to 1.30pm, and from 4.30am to 8.00pm. Besides you can find pharmacies that open 24 hours. Pharmacies follow a rolling late-hour schedule, which is published in the newspapers and the internet, and is posted at all pharmacies.

#### **OPENING HOURS FOR BUSINESS/SHOPS IN SEVILLE**

Most offices in Seville open at 9.00am and many close for a couple of hours in the afternoon, although this varies with companies. The most common business time-table is from Monday to Friday, from 9.30am to 1.30pm, and from 5.00pm to 8.00pm. Many shops also open on Saturdays from 9.30am to 1.30pm. Big shopping centers and department stores open

from 10.00am to 9.00pm or 10.00pm uninterruptedly, except Sundays and local holidays.

#### **OPENING HOURS FOR BANKS**

Banks are generally open Monday-Friday from 8.30am to 2.00pm, and sometimes on Saturday from 8.30am to 1.00pm.

#### **CURRENCY EXCHANGE**

There are many places to exchange currency, the banks being the ones with best rates. There are also foreign exchange outlets in the airports and even in some hotels and restaurants, although the rates are usually not so favourable. Withdrawing money at a cash point (ATM) is often the most convenient and economic way to obtain Euros and there are ATMs all over the city. Many are located inside banks or in their facades.

#### **CREDIT CARDS, TRAVELLERS CHEQUES**

Credit cards are widely accepted at establishments throughout Seville and these include Visa, EuroCard, Access, MasterCard and American Express. In some stores, you may be asked to enter your PIN (Personal Identification Number) into a keypad for security purposes. Some shops do not accept credit card payment for a small monetary amount. Travellers cheques, accompanied by a passport, are also accepted in most hotels, restaurants, and shops.

### ATMS (AUTOMATIC TELLER MACHINE)

There are ATMs almost everywhere, and most support Visa/Plus, Cirrus, and other popular systems. Just look for the signs next to the ATM or on the display itself. ATMs are easy to use here and all offer English as well as other languages.

#### **VAT REFUND**

How to get IVA (VAT) back on shopping: If a buyer's residence is outside the European Union, then he/she can claim back the tax on purchases, as long as they amount for more than €90.15 in each establishment. In order to do so, you should ask for a tax-free receipt, wherever you see the Spain Refund Tax-free Shopping logo, at the point of sale. The Tax-Free cheque must be stamped, always before the check-in. Show the goods to customs when leaving the country. You can claim your money in the SPAIN REFUND cash agents in airports and borders.

#### **CURRENCY CHOICE LOGO**

The Currency Choice logo next to a credit card terminal means that there you can pay by credit card in your own national currency. The amount on the receipt is the sum that will be debited to your bank. No hidden fees, no surprises when you get back home.

#### VISA INFORMATION

Anyone wishing to travel to and enter Spain must have a valid passport and/or the appropriate Spanish Visa. We recommend contacting your local Spanish consulate or Embassy for more information on these requirements.

For further information about Sevilla, please check www.infosevilla.com

The conference will be held at the:

#### **BARCELÓ RENACIMIENTO HOTEL**

Isla de la Cartuja, s/n E-41092

The avant-garde Barceló Renacimiento\*\*\*\*\* is a modern, topquality hotel located in Seville, on the Island of La Cartuja, on the banks of the Guadalquivir river, that is today home to the Cartuja scientific and technologic park. It is the best equipped hotel in the city to accommodate groups, conferences, congresses, and incentive trips, boasting its own 25-room Convention Center.

Conveniently located, just a few minutes away from Seville's historic center, the high-speed AVE train station and the airport close by, is an attractive option for both business travelers and people interested in urban sight-seeing.

Barceló Renacimiento's facilities include 25 meeting rooms and 2 atriums for events. The Convention Center Gran Sevilla was opened in 2002 and it provides fully equipped  $1,024m^2$  ideal for any kind of event. It can be turned into 3 independent rooms where natural light is very important. Besides, there is an exhibition area of  $800m^2$ .

Barceló Renacimiento hotel is member of the International Congress and Conventions Association (ICCA).

#### LOCATION

COORDINATES:

LAT: 37° 24' 35" N LONG: -5° 59' 43" W - E

A range of hotels (see map below) to suit all budgets and requirements are also within a short distance of the meeting venue.

#### How to Reach the Venue

Strategic location with an easy access, in a few minutes, both to the city's historical center and to the AVE train station or the airport.

Distance to the city center: 1-2 km. Distance to the airport: 10 km.

Train station: 20 min.

#### **BY BUS**

There is a good service city buses from/to the most important parts of the city, which takes around 10-20 minutes. Walking distance to bus stop: 3-5 minutes.

Please, see below section "Getting around" for further information.

#### BY TAXI

Taxi stops are located on several central streets and squares. Taxis, though, can be hailed any place in the city when they show the "libre" (free) sign or a green light. From 7.00am to 9.00pm Monday to Friday, taxis cost around €1.26 plus €0.87 per kilometer. At other times and on public holidays, it's €1.53 plus €1.07 per kilometer.

Taxi Phones: 954 675 555, 954 580 000, 954 622 222 www.taxisevilla.es, www.taxigiralda.es

#### RAILROAD/RAILWAY

The railroad transportation system connects all major urban centers. The **Santa Justa train station** serves as an important hub for connections between the Andalusia's main cities and all of the autonomous regions of Spain and Europe.

AVEs (high speed trains) connect to/from Cordoba (around  $\leqslant$ 34 to  $\leqslant$ 60, 40 minutes), Malaga ( $\leqslant$ 23 -  $\leqslant$ 45, 2½ hours), Madrid ( $\leqslant$ 85 -  $\leqslant$ 160, 2½ hours) or Barcelona ( $\leqslant$ 145 -  $\leqslant$ 260, 5½ hours). In addition to the AVE service, this modern station concentrates all railway traffic, with trains to various towns of the province, to all the capitals of Andalusia and to other Spanish cities such as Valencia, Alicante, and Cáceres.

The **Santa Justa Train Station** is located at Avda. Kansas City s/n. 41007 Sevilla, Information phone +34 902 320 320. International information phone: +34 902 243 402

For further information about train services and other train types and destinations please visit the website at www.renfe.es

#### ROADS

Highway and access roads and rapid beltways provide precise connections to all neuralgic points of the city and its surroundings. Seville has now become one of Spain's best connected cities by road, with highways connecting all Andalusia's main cities as well as Madrid and Portugal. Main access roads are the A-92. N-IV, A-4, and A-49.

#### **GETTING AROUND**

#### City Buses:

(Spanish name: *autobús*) Buses are the cheapest way to get around Sevilla. A single bus ride is €1.20, but you can buy a voucher with 10 trips (*bonobús*) from €7 at a newsstand or tobacco shop. The city bus network is based around four lines-C-1, C-2, C-3, and C-4- which follow circular routes, linking the main transport terminals and the city center. Four transversal lines and a series of radial lines which lead into the center from the four points of the compass complete the bus network.

You can pick up a bus route map, the Guía del Transporte Urbano de Sevilla, from tourist offices or from information booths at major stops (including Plaza Nueva, Plaza de la Encarnación and Avenida de Carlos V).

Information Phone: 010 (press 5) Web Site: www.tussam.es On the other hand, Seville has two bus stations, each providing services to separate cities:

- **Prado de San Sebastián**, just southeast of the Barrio de Santa Cruz, provides bus services to cities of Andalusia. Address: Manuel Vázquez Sagastizábal, s/n. Sevilla. Phone: +34 954 417 111

- Plaza de Armas, by the Cachorro's bridge, connects with the rest of Spain, the Province of Huelva, and Portugal. Address: Avenida del Cristo de la Expiración, s/n. - Sevilla. Phone: +34 954 908 040

#### Sightseeing tour buses:

Tour buses can be a great way to get around Seville. You have the option of traveling the full circuit and getting an overview of what to expect in the city or get on and off as many times as you want, seeing the sights as you go.

Web site: www.busturistico.com

#### Taxis:

Taxi stops are located on several central streets and squares. However, taxi can be hailed any place in the city when they show the *libre* (free) sign or a green light.

Many of the short cab rides cost between 3-6€. From the airport to the city center or the opposite there is now a flat rate. The fee is €21.89 during the day and €24.41 during holidays, Sundays or night (after 10pm).

Phones: +34 954 675 555 / +34 954 580 000 / +34 954 622 222

Web sites: www.taxisevilla.es, www.taxigiralda.es

#### Subway and tram:

(Spanish name: metro) Seville's subway system has only one line that goes from the west to the south part of the city and surrounding suburbs. A single ride is epsilon 1.30.

(Spanish name: tranvía metro centro) (T1) is a surface tram by the center of Seville that connects Plaza Nueva to Prado de San Sebastián bus station, with a total of 1.3km. This route covers the pedestrian area in the city center.

Web site: www.metrodesevilla.org

#### Bicycle:

(Spanish name: bicicleta) Sevici is the name of a community bicycle program in Seville. Its purpose is to cover the small and medium daily routes within the city in a climate friendly way. More than 250 stations and 2500 bikes will be available. The stations are situated throughout the inner-city with a distance of around 200 meters between each one, with many situated next to public transport stops to allow for intermodal use. The bikes can be borrowed from, and returned to, any station in the system, making it suitable for one way travel. Each station has between 10 and 40 parking slots to fix and lock the bicycle.

There is a short term subscription for tourists with an unlimited number of journeys during 7 consecutive days (a deposit of €150 is mandatory).

Web site: www.sevici.es

#### Other ways:

On foot: The city center of Seville is not very large and it is easy to walk to all the tourist spots, a lot of fun to walk around. The center has almost become completely car-free.

Horse-Drawn carriage tour: it is very typical way to get around Seville.

**River cruises along the Guadalquivir River:** the emblematic Andalusian river, the Guadalquivir is the only navigable river in Spain.

#### Sevilla Tourist Card

Sevilla Card, the Seville tourist card, will help you discover the city and enjoy your stay and save money. Its price is from €32. Some advantages with the card are:

- Free admission to most museums and monuments in the city and environs.

- Unlimited use of sightseeing buses.

- Boat rides on the Guadalquivir River.

- Isla Mágica Theme Park.

- Besides you will be able to enjoy discounts in shops, restaurants, shows, and leisure centers for adults and children.

- Guide/map with information about museums, services included, and participating establishments.

- A free "traditional tapa" as well as a drink.

Web site: www.sevillacard.es

# **CONFERENCE INFORMATION**

#### LANGUAGE

The official language of the meeting is English.

#### WEBPAGE

ICECS 2012 webpage: www.ieee-icecs2012.org

#### **REGISTRATION DESK**

Sunday, December 9th, 2012: 08:30 - 14:30

Monday, December 10th, 2012: 07:15 - 17:00

Tuesday, December 11th, 2012: 08:00 - 17:00

Wednesday, December 12th, 2012: 08:00 - 17:00

#### NAME BADGES

All participants and accompanying persons are asked to wear their name badges in a visible place. Entrance to sessions is restricted to registered delegates only. Entrance to meeting halls, poster and exhibition areas is granted to badge holders.

#### SPEAKERS BRIEFING

A digital projector and a PC are available in all conference rooms. Speakers should upload their presentations in advance at the Conference Registration Desk with the help of technical staff. ICECS Organization recommends speakers to use the computers in the conference rooms, which have installed Windows 7 OS with Windows Power Point 2010 and Adobe Acrobat PDF Reader. All presentation files will be deleted at the end of the conference and no copy will be saved.

The time scheduled for each presentation is about 17 min for lectures and 3-4 min for poster briefing. Questions to the authors are very welcome and can be raised at the end of the presentation or at the end of the session, according to the chairman's decision. Chairmen and speakers are requested to respect scheduled times. Authors should meet their chairman in the session room 15 min ahead the respective sessions.

Speakers are kindly requested to present a short bio at the Conference Registration Desk the day of arrival. This information is useful for the chairman to correctly introduce the speaker of the paper.

#### INTERNET ACCESS

Wireless internet access will be available at the conference venue without charge. More info will be provided at the Conference Registration Desk.

#### **CONFERENCE PROCEEDINGS**

All participants will receive an electronic copy of the ICECS 2012 Proceedings in a USB flash drive.

#### **BEST PAPER AWARD**

Papers presented at the conferences will be considered for the Best Paper Award. The jury will be composed by members of the

# **CONFERENCE INFORMATION**

Organization Committee and of the Technical Program Committee. The award delivery will take place during the closing ceremony.

#### INSURANCE DISCLAIMER

Participants are responsible for their own insurance. The organizers cannot take responsibility for any accident, loss or damage to participants or their property during the event.

#### **COMPLAINTS**

While we hope that your time at the conference is enjoyable, if you encounter a problem during your stay, please report it to the registration desk as soon as possible. The conference team will make every effort to rectify the issue.

# **MEALS AND REFRESHMENTS**

All meals and refreshments will be served at scheduled times during the conference program.

Colón

#### Monday, December 10th, 2012

Morning refreshments In front of Room Sevilla I

Lunch

Afternoon refreshments In front of Room Sevilla I

Welcome Reception Hotel Barceló

#### TUESDAY, DECEMBER 11TH, 2012

Morning refreshments In front of Room Sevilla I

Lunch Colón

Afternoon refreshments In front of Room Sevilla I

Gala Dinner\* Abades Triana Restaurant

### WEDNESDAY, DECEMBER 12TH, 2012

Morning refreshments In front of Room Sevilla I

Lunch Colón

Afternoon refreshments In front of Room Sevilla I

Participants with special dietary requirements who have not previously informed about it please contact to the registration desk in order to provide an alternative menu.

<sup>\*</sup>The Gala dinner is included in the registration conference fee. To buy additional tickets, please contact the registration desk.

## SOCIAL PROGRAM

#### Monday, December 10th, 2012

#### WELCOME COCKTAIL

The Welcome Cocktail will take place at Hotel Barceló (conference venue) on December 10th, at 19:30.

A hotel with a unique beauty, set on three circular buildings or atriums surrounded by gardens, open spaces, and an incomparable Guadalquivir river view.

Barceló revival has become an essential reference in Seville for holding conventions, conferences, and all kind of international events.

Don't miss this opportunity to know your fellow participants to the Conference ICECS 2012. Enjoy it!

# TUESDAY, DECEMBER 11TH, 2012

#### **GALA DINNER**

The Gala Dinner program will include a panoramic city sightseeing tour and a visit to the Alcázar.

The local organization will provide buses for the transportation from Hotel Barceló. We will leave the conference venue from 19:30 to 20:00. Attendees who prefer, can join us at the door of the Lions (Puerta de los Leones), in the Alcázar at 20:00.

Seville is the artistic, cultural, and financial capital of the southern Spain. The city is a historical masterpiece full of Islamic monuments, gardens, and flamenco festivals.

We will begin our city sightseeing tour from Hotel Barceló, with a view of the most relevant monuments and sights of the city.

# **SOCIAL PROGRAM**

After that, we will visit the Alcázar, also called Real Alcázar or Reales Alcázares de Sevilla. This beautiful place began to take its present form after the conquest in 713 of Seville by the Arabs, who used Alcázares as the residence of its leaders from 720. After the Reconquista in 1248, it was the accommodation of King Fernando III, taking on the habit of lodging the successive monarchs.

It is now used as a place of accommodation for members of the Royal Family and dignitaries who visit the city. The important events that take place in the city are often held in the Alcázar. The Alcázar and its gardens are one of the main attractions of the Seville.

The Gala Dinner will be held at Abades Triana Restaurant.

An exquisite place, located in Triana's heart, in front of the Golden Tower (Torre del Oro), where you can enjoy the best dinner and the Guadalquivir river views.

Finally, we will return to Hotel Barceló for resting.

# **OPTIONAL LEISURE ACTIVITIES**

#### **SIGHTSEEING TOURS AND ACTIVITIES**

You have the opportunity to make different sightseeing tours and activities offered at a reduced price for ICECS attendees.

To register and get more information, please visit http://www.ieee-icecs2012.org/registro/activities/ registration\_form.php

#### **ACTIVITIES (DECEMBER 8-12, 2012)**

#### Sevilla Alcázar, El Salvador (guided morning tour)

Departure Days: Sunday, Wednesday, Friday

Duration: 31/2 hours

Departure Point: Hotel or place assigned by the agency

€37 Tax Included

# Sevilla Cathedral, Giralda Tower, and Basílica Macarena (guided morning tour)

Departure Days: Monday, Tuesday, Thursday, Saturday

Duration: 3½ hours

Departure Point: Hotel or place assigned by the agency

€37 Tax Included

#### Sevilla Bullring and River Cruise (guided afternoon tour)

Departure Days: Sunday, Monday, Wednesday, Friday

Duration: 3 hours

Departure Point: Hotel or place assigned by the agency

€32 Tax Included

#### Monumental Sevilla (morning tour)

Departure Days: Saturday, Monday, Tuesday, Thursday

Duration: 3 hours

Departure Point: Main door of the Starbucks cafe - San

Fernando Street 1 (Puerta Jerez)

€22 Tax Included

#### Typical Sevilla

Departure Days: Sunday, Wednesday, Friday

Duration: 3½ hours

Departure Point: Main door of the Starbucks cafe - San

Fernando Street 1 (Puerta Jerez)

€29 Tax Included

#### Roman City of Itálica (afternoon tour)

Departure Days: Saturday, Tuesday, Thursday

Duration: 4 hours

Departure Point: Hotel or place assigned by the agency

€29 Tax Included

#### Noche Sevillana

Departure Days: Daily

# **OPTIONAL LEISURE ACTIVITIES**

Duration: 3 hours

Departure Point: Hotel or place assigned by the agency

€50 Tax Included

#### Tickets River Cruise + Flamenco Show (afternoon)

Departure Days: daily Duration: 3 hours

Departure Point: Boat: Muelle Torre del Oro / Flamenco: María

Auxiliadora Avenue 18 B

€45 Tax Included

#### Tickets River Cruise + Flamenco Show (night)

Departure Days: daily Duration: 3 hours

Departure Point: Boat: Muelle Torre del Oro / Flamenco: María

Auxiliadora Avenue 18 B

€45 Tax Included

#### Córdoba

Departure Days: Saturday, Tuesday, Thursday

Duration: 9 hours

Departure Point: Hotel or place assigned by the agency

€95 Tax Included

#### Jerez & Cádiz

Departure Days: Tuesday, Thursday

Duration: 9 hours

Departure Point: Hotel or place assigned by the agency

€105 Tax Included

#### Hop On Hop Off Tour Bus

Departure Days: Daily Duration: 24 hours

Departure Point: Torre del Oro

€16 Tax Included

#### Sevilla Walking Tour + River Cruise

Departure Days: Daily Duration: 2½ hours

Departure Point: Torre del Oro

€32 Tax Included

#### Walking Tour + Horse-Drawn Carriage Tour

Departure Days: Daily Duration: 2½ hours

Departure Point: Plaza de España

€54 Tax Included

#### Romantic Sevilla

Departure Days: Daily

## **OPTIONAL LEISURE ACTIVITIES**

Duration: 2 hours

Departure Point: Plaza de España

€85 Tax Included

#### MUSEUMS IN SEVILLE

Free entry for EU citizens. Non-EU citizens: €1.50 to the following museums:

- Museo Arqueológico de Sevilla (Archaeological Museum) www.museosdeandalucia.es/cultura/museos/MASE/?lng=en

- Museo de Bellas Artes (Museum of Fine Arts) www.museosdeandalucia.es/cultura/museos/MBASE/ ?lng=en

- Museo de Artes y Costumbres Populares (Museum of Arts and Traditions)

- www.museosdeandalucia.es/cultura/museos/MACSE/

- Conjunto Arqueológico Itálica (Archaeological Ensemble Italica)

- www.museosdeandalucia.es/cultura/museos/CAI/

- Conjunto Arqueológico de Carmona (Archaeological Ensemble Carmona)

- www.museosdeandalucia.es/cultura/museos/CAC/?lng=en

#### Non-free entry:

Monasterio de la Cartuja (Cartuja Monastery) and Centro Andaluz de Arte Contemporáneo (Andalusia Contemporary Art Center)

www.juntadeandalucia.es/cultura/caac/english/frame.htm €1.80 Visit the monument or to the temporary exhibitions €3.01 Complete visit

# PLENARY LECTURES

#### Monday, December 10th, 2012

# ULTRA-LOW-POWER CIRCUIT TECHNIQUES FOR IMPLANTED/MEDICAL APPLICATIONS

#### Prof. Yusuf Leblebici

Director of the Microelectronic Systems Laboratory at the École Polytechnique Fédérale de Lausanne (EPFL)

**Prof. Yusuf Leblebici** received the B.Sc. and M.Sc. degrees in electrical engineering from Istanbul Technical University, Istanbul, Turkey, in 1984 and 1986, respectively, and the Ph.D. degree in electrical and computer engineering from the University of Illinois, Urbana-Champaign (UIUC), in 1990.

Between 1991 and 2001, he worked as a

faculty member at UIUC, at Istanbul Technical University, and at Worcester Polytechnic Institute (WPI). In 2000-2001, he also served as the Microelectronics Program Coordinator at Sabanci University. Since 2002, he has been a Chair Professor at the Swiss Federal Institute of Technology in Lausanne (EPFL), and director of Microelectronic Systems Laboratory. His research interests include design of high-speed CMOS digital and mixedsignal integrated circuits, computer-aided design of VLSI systems, intelligent sensor interfaces, modeling and simulation of semiconductor devices, and VLSI reliability analysis. He is the coauthor of four textbooks, namely, Hot-Carrier Reliability of MOS VLSI Circuits (Kluwer Academic Publishers, 1993), CMOS Digital Integrated Circuits: Analysis and Design (McGraw Hill. 1st Edition 1996, 2nd Edition 1998, 3rd Edition 2002), CMOS Multichannel Single-Chip Receivers for Multi-Gigabit Optical Data Communications (Springer, 2007) and Fundamentals of High Frequency CMOS Analog Integrated Circuits (Cambridge University Press, 2009), as well as more than 200 articles published in various journals and conferences.

Dr. Leblebici has served as an Associate Editor of IEEE Transactions on Circuits and Systems II and IEEE Transactions on VLSI Systems. He has also served as the general co-Chair of the 2006 European Solid-State Circuits Conference, and the 2006 European Solid State Device Research Conference (ESSCIRC/ESSDERC). He has been elected as Distinguished Lecturer of the IEEE Circuits and Systems Society for 2010-2011 and is an IEEE Fellow.

# **PLENARY LECTURES**

# TUESDAY, DECEMBER 11TH, 2012 FROM DATA TO INSIGHT

Dr. Ellen J. Yoffa

Director, Information & Interaction IBM T. J. Watson Research Center Yorktown Heights, New York, USA

#### Abstract

In our daily lives, we're surrounded by massive amounts of rich multimedia data of all kinds. The challenge is to interpret this data and use it to make intelligent decisions in real time. In this talk, I'll highlight a selection of projects from the Information & Interaction team at IBM Research. These projects explore technologies for human language understanding, image processing, and social network analysis. This research aims to extract insight from the data around us.

**Dr. Ellen J. Yoffa** is Director of Information & Interaction at the IBM T. J. Watson Research Center. She leads research in a spectrum of technologies from mobile to human language and image analytics to social networking. She is past President of the IEEE Circuits and Systems Society and currently serves on several IEEE committees, including the

Technical Activities Strategic Planning Committee, TAB Financial Committee and the IEEE Ethics & Member Conduct Committee, and has been elected to the 2014 IEEE Board of Directors. She received the 2009 IEEE Circuits and Systems Society Meritorious Service Award. Dr. Yoffa spent many years in electronic design automation research and chaired the 1997 IEEE/ACM Design Automation Conference. She was awarded the 2006 Marie R. Pistilli Achievement Award for Women in Electronic Design Automation. She received a BS and PhD in Physics at the Massachusetts Institute of Technology and is an IEEE Fellow.

### PLENARY LECTURES

#### WEDNESDAY, DECEMBER 12TH, 2012

# COMPRESSED SENSING ANALOG-TO-DIGITAL CONVERSION

Prof. Michael P. Flynn

Dept. of Electrical Engineering & Computer Science (EECS) at the University of Michigan

#### Abstract

The amount of digital information in the world has increased dramatically over the past few years. As the portability and computing power of electronics has improved a need for both high-capacity data storage centers and large wireless communication infrastructures has arisen. However. transmission of data often dominates the energy consumption portable electronics. Although technology scaling has reduced the energy cost per transistor in digital circuits, and has improved the overall energy efficiency of digital computing, the energy cost associated with data communication dominates. In order to match pace with the available computing resources, the energy efficiency of data transmission must improve. In addition, the energy efficiency of data acquisition through analog-to-digital conversion must also improve to growth in digital information support the processing. Compressed sensing promises to improve the energy efficiency of sensing systems, and of wireless communication and analogto-digital conversion. This lecture reviews the concepts behind compressed sensing and surveys some recent approaches to compressed sensing in analog to digital conversion.

Prof. Michael P. Flynn received the Ph.D. degree from Carnegie Mellon University in 1995. From 1988 to 1991, he was with the National Microelectronics Research Centre in Cork, Ireland. He was with National Semiconductor in Santa Clara, CA, from 1993 to 1995. From 1995 to 1997 he was a Member of Technical Staff with Texas

Instruments, Dallas, TX. During the four-year period from 1997 to 2001, he was with Parthus Technologies, Cork, Ireland. Dr. Flynn joined the University of Michigan in 2001, and is currently Professor.

Michael Flynn is a 2008 Guggenheim Fellow. He received the 2011 Education Excellence Award and the 2010 College of Engineering Ted Kennedy Family Team Excellence Award from the College from Engineering at the University of Michigan. He

### **PLENARY LECTURES**

received the 2005-2006 Outstanding Achievement Award from the Department of Electrical Engineering and Computer Science at the University of Michigan. He received the NSF Early Career Award in 2004. He received the 1992-93 IEEE Solid-State Circuits Pre-doctoral Fellowship. He is an Associate Editor of the IEEE Journal of Solid State Circuits (JSSC) and serves on the Technical Program Committees of the International Solid State Circuits Conference (ISSCC) and the IEEE Symposium on VLSI Circuits. He formerly served on the program committee of the Asian Solid-State Circuits Conference was Associate Editor of the IEEE Transactions on Circuits and Systems II from 2002 to 2004.

#### **TUTORIAL 1**

# ADVANCES IN TIME-ENCODED ANALOG SIGNAL PROCESSING AND DATA CONVERSION

#### Luis Hernandez, Susana Paton, Enrique Prefasi

Electronics Department of Carlos III University, Madrid, Spain

#### Pieter Rombouts

Electronics and Information Systems Department of Gent University, Belgium

Sunday, December 9th, 2012 (9:00 - 13:00) Room Andalucía 5

#### Abstract

The feature size improvement of nanometer CMOS technology represents an enhancement of speed and power consumption for digital circuits but at the expense of analog performance degradation. Time encoding techniques are one of the research trends in analog signal processing to overcome this problem and ease an accurate representation of analog signals within nanometer CMOS chips operating at very low voltage. In essence, time encoding techniques map a continuous time signal into a pulse coded signal. As long as pulse streams are formed of discrete events, some signal processing concepts are needed to bridge both kind of representations. Most time encoding techniques used so far stem from classical pulse modulations such as PWM, PPM and from non uniform sampling schemes. These techniques are known from a signal processing point of view since long ago, but its particular application may not be familiar to analog circuit designers. This tutorial will explore the basics of time encoding techniques and especially, its application to data conversion.

An introductory presentation will review the signal processing concepts involved in time encoding techniques and its implications when applied to CMOS circuit design. A second presentation will discuss the design of continuous time sigma delta converters that rely on time encoding to replace multibit internal ADCs and DACs. This presentation will cover both system and circuit level aspects. Finally, we will show the recent advances in time encoded signal processing using mostly digital elements such as gated and voltage controlled ring oscillators, variable delay gates and asynchronous digital circuitry.

#### **Topics**

- Introduction to Time Encoded Signal Processing (P. Rombouts)

- Design of Continuous Time Sigma Delta Modulators with Time Encoded Quantizers (S. Paton)

- CMOS Circuit Design for Time Encoded Analog Signal Processing (E. Prefasi)

- Time Encoded Signal Processing Using Mostly Digital Circuitry (L. Hernandez)

#### **TUTORIAL 2**

### SILICONIZED PHOTONICS-ELECTRONICS AS AN EMERGING TECHNOLOGY

Henry H. Radamson, Lars Thylén KTH Royal Institute of Technology, Sweden

Sunday, December 9th, 2012 (9:00 - 13:00) Room Andalucía 6

#### Abstract

Silicon photonics is an emerging technology offering novel solutions in different areas such as optical communications, optical computer interconnects, sensing, bio-applications, all requiring highly integrated novel photonics-electronics. Silicon photonics-based communication has many advantages over electric wires for multiprocessor and multicore macro-chip architectures including high bandwidth data transmission, high speed and low power consumption, not possible with all electronics solutions at the required high transmission rates. Following the INTEL's concept to "siliconize" photonics, silicon device technologies should be able to meet the requirements for six main building blocks for realization of the emerging optical interconnects technology: light generation, guiding of light including electronically controllable wavelength selectivity. light modulation for signal encoding, detection, low cost assembly including optical connecting of the devices to the real world and finally the electronic control systems.

The silicon-based materials, mainly alloying Si with other elements in the group IV, in form of quantum well or dot structures demonstrate new photonic properties as well as carrier transport, paving the path for a paradigm shift which is along with the semiconductor industry's needs in the near future. For example, novel Sn-GeSi materials have shown the possibility of having direct bandgap property. Epitaxial growth of strained (or relaxed) Sn-GeSi materials on Si for lasing and detection of telecommunication wavelengths is an on-going development.

This tutorial includes the all important issue of light generation and detection in group IV materials, an overview of waveguide silicon photonics devices, including the possibility of employing the silicon compatible electro-optic polymers for high speed, low power phase modulation, especially important in view of the quest for advanced modulation formats and then presents how this photonics technology can be developed into monolithically integrated photonics-electronics technology on silicon, which can be obtained when Sn-GeSi alloys are integrated in the chip. The tutorial will also present briefly the CMOS part of the chip in the More than Moore approach of the roadmap. The difficulties to achieve the next technology node (16 nm node by 2014 timeframe) will be shortly overviewed. The future down-scaling of transistors is discussed, when the quantum tunneling will occur and limits the functioning of devices (no matter of the applied material). This tutorial will provide insights into a potential Si electronics-photonics roadmap scenario when new material systems and concepts are introduced.

#### **Topics**

- Building lasers and detectors from group IV materials (H. Radamson)

- Modulators, switches and WDM devices: Plasmonics and electrooptic polymers for Si based low power nanophotonics integrated photonics fabrics for communications and interconnect (L. Thylen)

- Merging the best of two worlds: Issues in monolithic nanoscale photonics-electronics integration (H. Radamson)

#### **TUTORIAL 3**

# RF CMOS WIRELESS RECEIVERS FOR 402MHZ MEDICAL IMPLANTABLE COMMUNICATION SYSTEMS

#### Sherif Mohamed, Yiannos Manoli

Fritz Huettinger Chair of Microelectronics, IMTEK Albert-Ludwig-University Freiburg

Sunday, December 9th, 2012 (9:00 - 13:00) Room Andalucía 7

#### Abstract

With the increasing number of portable and implantable personal health care devices, there is a strong demand to

control their communication in a single wireless network. The advances of the communication technologies have made these devices easier to use. One of the problems which render the using of these devices is the power consumption. There are wireless and wireline approaches to implement the BSN network. Recently, wireless body-area-network (WBAN) is getting more and more attention. WBAN is composed of numerous healthcare devices or physiological sensors and also provides wireless connectivity among them for the continuous and ambulatory health care. WBAN technologies have been an active research area, and it is categorized into wearable BAN BAN. The implantable wearable BAN is only communication among the on-body devices such as electrocardiogram (ECG). electroencephalography electromyography (EMG), and body temperature sensors. On the other hand, the implantable WBAN connects the implanted devices such as pacemaker with on-body controller.

For the data transmission with implanted medical devices, the 402-405 MHz, medical implant communication service (MICS) Transceivers, NB PHY, is adapted for the in-body devices. MICS standard is divided into 10 channels for listen-before-talk (LBT) protocol as mainly discussed by Federal Communications Commission (FCC). This needs 10ms for scanning the channel before each MICS communication starts.

#### Topics